### **Aalborg Universitet**

## **Analysis and Modeling of Transformerless Photovoltaic Inverter Systems** Kerekes, Tamas Publication date: 2009 Link to publication from Aalborg University Citation for published version (APA): Kerekes, T. (2009). Analysis and Modeling of Transformerless Photovoltaic Inverter Systems. Aalborg Universitet: Institut for Energiteknik, Aalborg Universitet.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## Analysis and Modeling of Transformerless Photovoltaic Inverter Systems

by

Tamás Kerekes

Dissertation submitted to the Faculty of Engineering, Science & Medicine at Aalborg University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Aalborg University Institute of Energy Technology Denmark, August 2009 Aalborg University Institute of Energy Technology Pontoppidanstraede 101 DK-9220 Aalborg East Denmark

Copyright © Tamás Kerekes, 2009 Printed in Denmark by Second print,

ISBN: 978-87-89179-85-8

## **Preface**

This thesis is written in the frame of two research projects: the first, entitled "Transformerlose solcelle invertere", was financially supported by the Eltra PSO-F&U contract nr. 5780 signed between Aalborg University and Energinet in cooperation with Powerlynx A/S, now Danfoss Solar A/S. The second part of the research, entitled "Electrical energy conversion and condition-ECON2", was supported by the EU framework entitled "Marie Curie Host Fellowships for Early Stage Researcher Training", financially supported by the EC Contract MEST-CT-2004-504243. Acknowledgements are given to Aalborg University and the above mentioned institutions for their financial support.

The research was carried out under the supervision of Professor Remus Teodorescu from Institute of Energy Technology (IET) at Aalborg University. My deepest gratitude goes to my supervisor for his guidance and professional support during the elaboration of the work done in this thesis.

I would like to express my sincere thanks to Dr. Christian Klumpner and Dr. Mark Sumner for their guidance and support during my one-year stay at Nottingham University. I'm also grateful to Dr. Marco Liserre from Politecnico di Bari for his kindness and professional guidance during my six month stay at the Dipartimento di Elettrotecnica ed Elettronica. I would also like to thank Uffe Borup, from Danfoss Solar A/S, for participating in the steering meetings and for his active support.

I want to thank to all my colleagues from Institute of Energy Technology for their friendly companionship which guided me through life at Aalborg University. Special thanks go to Dr. Pedro Rodriguez and Professor Vassilios Agelidis for their unselfish help and moral support, during their stay at IET. Also many thanks to all my fellow PhD students, who assisted me many times and gave me support in different ways. In particular, I thank to Dezső Séra, Mihai Ciobotaru and Máthé László for their friendly help and encouragement. I would also like to thank Gerardo Vazquez from Universitat Politecnica de Catalonya for sharing his experience and time with me during his visit at IET.

And, last but not least, I want to express my deepest gratitude to my wife Erzsébet Kerekes and to my entire family in Romania for the substantial and continuous support which I have received during the elaboration and finalization of this work.

Tamás Kerekes August 2009; Aalborg

### Abstract

The need for a cleaner environment and the continuous increase in power demands makes decentralized renewable energy production, like solar and wind, more and more interesting. Decentralized energy production using solar energy could be a solution for balancing the continuously-increasing power demands. This continuously increasing consumption overloads the distribution grids as well as the power stations, therefore having a negative impact on power availability, security and quality. One of the solutions for overcoming this is the grid-connected photovoltaic (PV) system.

PV inverter systems can be improved in terms of efficiency using transformerless topologies, but new problems related to leakage current need to be dealt with.

The work presented in this thesis deals with analyzing and modeling of transformerless PV inverter systems regarding the leakage current phenomenon that can damage solar panels and pose safety problems.

The major task of this research was the investigation and verification of transformerless topologies and control strategies to minimize the leakage current of PV inverter topologies in order to comply with the standard requirements and make them safe for human interaction.

The thesis is divided into two parts: Part I – Report and Part II – Publications. Part I is a summary report of the work done throughout the research and contains 6 chapters.

Chapter 1: Introduction, focuses on the background and motivation regarding the research done in this thesis. Furthermore, the objectives and limitations of the project are enumerated. The chapter finishes with the outline of the thesis.

Chapter 2: Overview of grid connected PV systems, gives an overview about grid connected PV inverters, focusing on transformerless inverters and related safety issues. The parasitic capacitance of several commercial mono- and multi-crystalline PV panels has been measured, and an appropriate value has been defined for use in the simulations. Also, two commercial current sensors that can be used for leakage current measurement, have been tested and the results are presented in Appendix A.

A detailed investigation of different inverter topologies regarding the ground leakage current is described in Chapter 3: Investigation of transformerless topologies, showing the ground voltage and leakage current for the analyzed topologies, concluding with whether the topology is suited for transformerless PV systems.

Chapter 4: Common mode voltage in PV inverter topologies, explains the common-mode behavior of single and three-phase PV inverter topologies by presenting a comprehensive analysis of the single and three-phase transformerless converter with

respect to the problem of the leakage current that flows through the parasitic capacitance of the PV array.

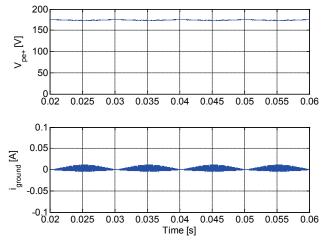

In Chapter 5: H-Bridge Zero Voltage Rectifier topology, a new inverter called H-Bridge Zero Voltage Rectifier (HB-ZVR) is proposed, where the mid-point of the DC link is clamped to the grid only during the Zero Voltage period by means of a diode rectifier bridge and one switch. A comparison of known transformerless topologies and the HB-ZVR is performed using simulations, focusing on the voltage to earth harmonics and ground leakage current. Furthermore, experimental results are shown, confirming the simulations, and finally, the efficiency curve of the compared topologies is detailed.

In Chapter 6: Conclusion, the final conclusion is presented, based on the theoretical and experimental results performed. Also a list is given, detailing the contributions presented in this thesis. Additionally, guidelines for future work are given.

The second part of the thesis: Part II – Publications contains the papers that have been published during the period of the research. The articles describe in detail the methods, simulations and the experimental results that make up the backbone of the work described in this thesis.

## Dansk resumé

Behovet for et renere miljø og den fortsatte stigning i ydelse krav gør decentral produktion af vedvarende energi, såsom solcelle og vindenergi, mere og mere interessant. Decentral energiproduktion ved hjælp af solenergi kan være en løsning for at afbalancere det stadigt stigende strøm behov. Det stadigt stigende forbrug belaster distributionsnettet, samt kraftværker, derfor har forbruget en negativ indvirkning på magten af pålidelighed, sikkerhed og kvalitet. En af de løsninger for at overvinde dette er nettilsluttet solcelle system.

Solcelle inverter systemer kan forbedres ved hjælp af transformerløse topologier, men nye problemer i forbindelse med lækstrøm har behov for at blive behandlet.

I denne forbindelse præsenteres denne afhandling der beskæftiger sig med analyse og modellering af transformerløse solcelle inverter systemer med fokus på lækstrøms fænomener, der kan skade solpaneler og udgøre en sikkerheds-risiko.

Den største opgave i denne afhandling blev undersøgelsen og verifikation af transformerløse topologier og kontrolstrategier, der vil minimere lækstrøm af solcelle inverter topologier for at overholde standardkrav og gøre dem sikre for menneskelig interaktion.

Afhandlingen er opdelt i to dele: Del I - Rapport og Del II - Publikationer. Del I er en sammenfattende rapport over det udførte arbejde i hele forskningsperioden og indeholder 6 kapitler.

Kapitel 1 fokuserer på baggrunden og motivationen i forbindelse med forskningen beskrevet i denne afhandling. Desuden er mål og begrænsninger for projektet er fremsat, afsluttende med et overblik over afhandlingen.

Kapitel 2 giver en oversigt over nettilsluttede solcelle invertere, der fokuserer på transformerløse frekvensomformere og de relaterede sikkerhedsspørgsmål. Den parasitiske kapacitans af flere kommercielle mono-og multi-krystallinske solcelle paneler er blevet målt, og en repræsentativ værdi er fastsat til anvendelse i simuleringerne. Også to nuværende sensorer, som vil kunne bruges til lækstrøm måling, er blevet testet, og resultaterne præsenteres i tillæg A.

En detaljeret undersøgelse af forskellige inverter topologier med hensyn til jordlækstrom er beskrevet i kapitel 3, der viser DC til jord potentialet og lækstrømmen for de analyserede topologier, indgåelse hvis topologi er velegnet til transformerløse solcelle anlæg.

Kapitel 4 forklarer common-mode opførsel af en og tre-fase solcelle inverter topologier ved at fremlægge en omfattende analyse af enkelt og tre-fase transformerløse konvertere med hensyn til problemet med lækstrøm, der løber gennem den parasitiske kapacitans i solcelle anlæg.

I kapitel 5 er en ny inverter kaldet H-Bridge Zero Voltage Rectifier (HB-ZVR) foreslået, hvor DC-link midtpunktet af er fastholdt på frekvensomformeren kun under nul spænding perioden ved hjælp af en diode ensretter og en transistor. En sammenligning af kendte transformerløse topologier og HB-ZVR udføres ved hjælp af simulering, der fokuserer på spændingen til jord, og jordlækstrøm. Desuden er den givet eksperimentelle resultater, der bekræfter simuleringerne, og sluttelig præsenteres virkningsgraden for de forskellige topologier.

I kapitel 6 præsenteres den endelige konklusion baseret på de teoretiske og eksperimentelle resultater. Derudover findes også en angivelse at de bidrag der præsenteres i denne afhandling. Derudover er der også givet retningslinjer for fremtidige arbejde.

Den anden del af afhandlingen: Part II - Publikationer indeholder de artikler, der er publiceret løbet af denne forskningsperiode. Artiklerne beskriver i detaljer, de metoder, de simuleringer, eller de eksperimentelle resultater, der udgør grundlaget i det arbejde, der er beskrevet i denne afhandling.

## Table of contents

|                                                     | III  |

|-----------------------------------------------------|------|

|                                                     | V    |

|                                                     | vi   |

|                                                     | ix   |

|                                                     | xiii |

| j                                                   | XV   |

| Introduction                                        | 1    |

| Background and motivation                           | 1    |

| Grid connected PV systems                           | 2    |

| Aims of the project                                 | 3    |

| Problem formulation                                 | 3    |

| Objectives                                          | 3    |

| Limitations                                         | 4    |

| Main contributions                                  | 4    |

| Outline of the thesis                               | 5    |

| List of publications                                | 7    |

| Overview of grid connected PV systems               | 9    |

| Introduction                                        | 9    |

| Central inverters                                   | 10   |

| String inverters                                    | 11   |

| Module inverters                                    | 11   |

| Multi-String inverters                              | 11   |

| Grid requirements                                   | 12   |

| Transformerless PV inverters                        | 14   |

| Transformerless inverter topologies                 | 17   |

| Parasitic capacitance of PV arrays                  | 24   |

| Leakage ground current                              | 26   |

| Summary                                             | 28   |

| Investigation of transformerless topologies         | 29   |

| Introduction                                        | 29   |

| Single-phase topologies                             | 31   |

| H-Bridge topology with Bipolar PWM                  | 31   |

| H-Bridge topology with Unipolar PWM                 | 33   |

| H-Bridge topology with hybrid modulation            | 35   |

| HERIC topology from Sunways                         | 36   |

| H5 topology from SMA                                | 37   |

| Single-phase topology with DC decoupling (Ingeteam) | 39   |

|                                                     |      |

| 3.2.7      | Half bridge topology                                             | 40 |

|------------|------------------------------------------------------------------|----|

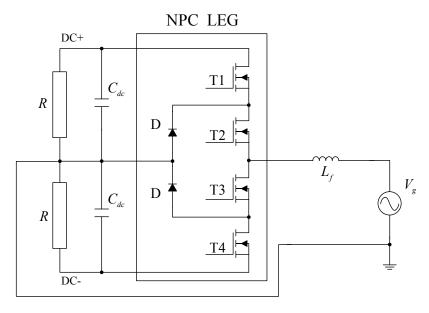

| 3.2.8      | Neutral Point Clamped topology                                   | 41 |

| 3.3        | Three-phase topologies                                           | 42 |

| 3.3.1      | Three-phase Full Bridge                                          | 42 |

| 3.3.2      | Full Bridge with Split Capacitor                                 | 44 |

| 3.3.3      | Full Bridge with Split Capacitor using staggered modulation      | 44 |

| 3.3.4      | Three-phase Neutral Point Clamped                                | 44 |

| 3.4        | DC current injection control in case of transformerless systems  | 45 |

| 3.5        | Summary                                                          | 46 |

| Chapter 4  | Common mode voltage in PV inverter topologies                    | 47 |

| 4.1        | Introduction                                                     | 47 |

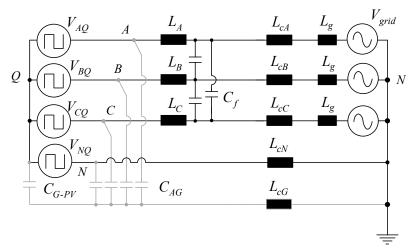

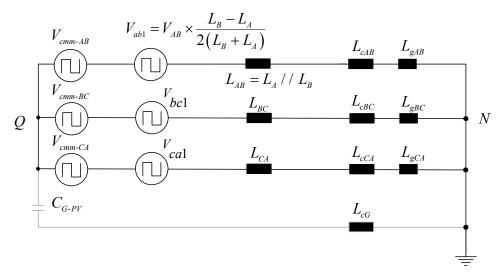

| 4.2        | Common-mode voltage in three-phase systems                       | 49 |

| 4.2.1      | Model of common-mode and differential-mode voltages              | 49 |

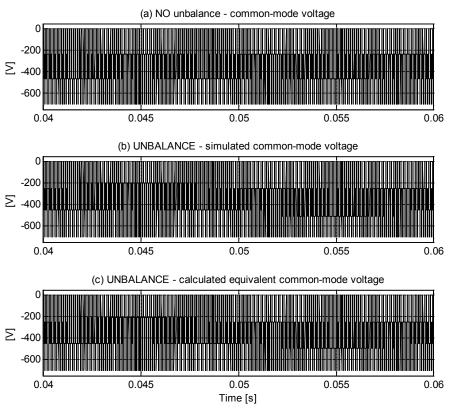

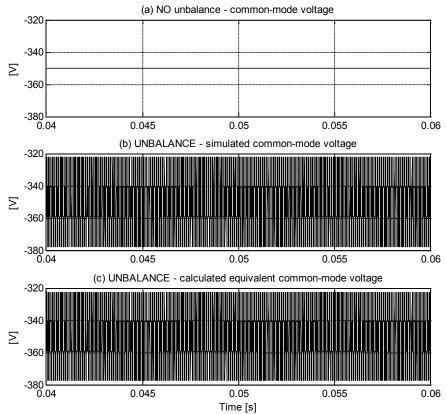

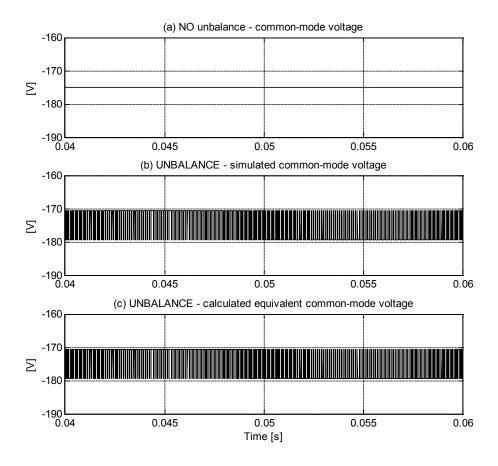

| 4.2.2      | Leakage current in case of imbalance filter inductance condition | 50 |

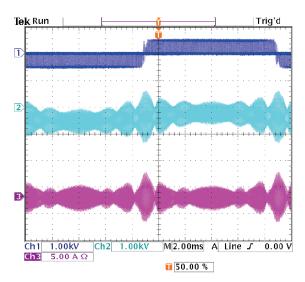

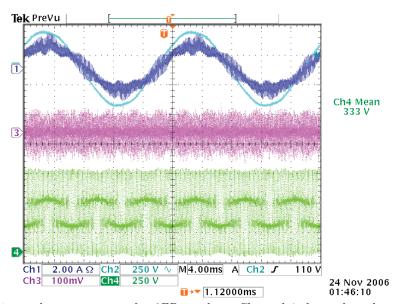

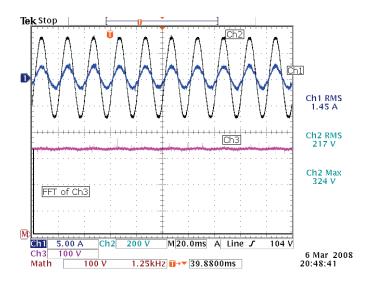

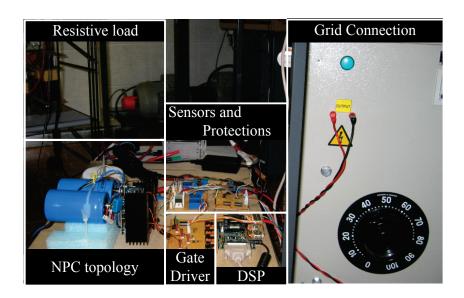

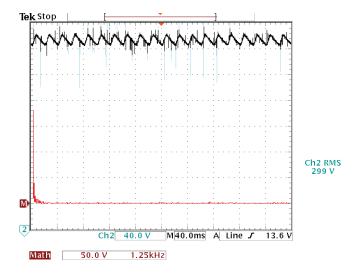

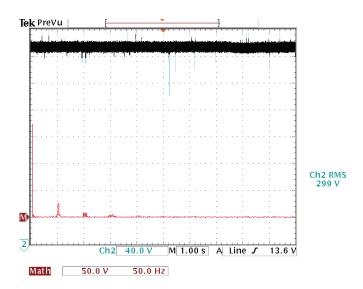

| 4.2.3      | Experimental results (inverter mode)                             | 52 |

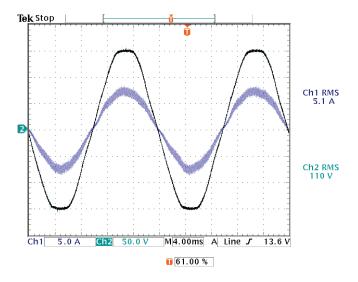

| 4.2.4      | Experimental results (rectifier mode)                            | 52 |

| 4.3        | Common-mode voltage in single-phase systems                      | 55 |

| 4.4        | Summary                                                          |    |

| Chapter 5  | H-Bridge Zero Voltage Rectifier topology                         | 57 |

| 5.1        | Introduction                                                     | 57 |

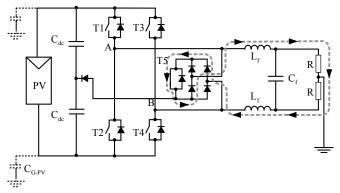

| 5.2        | Transformerless topology analysis                                | 57 |

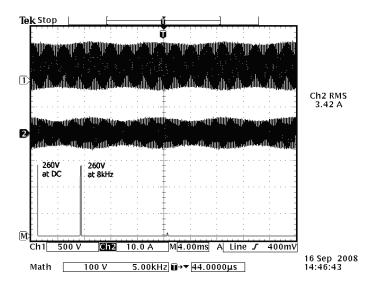

| 5.2.1      | H-Bridge with unipolar switching                                 | 59 |

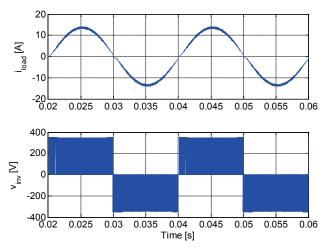

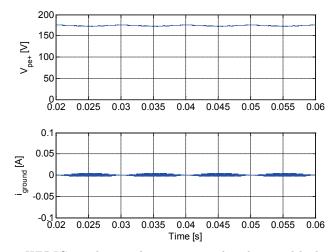

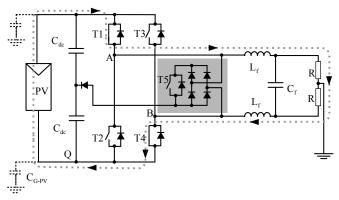

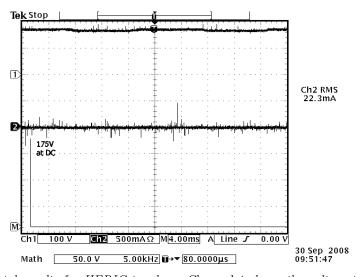

| 5.2.2      | HERIC – Highly Efficient and Reliable Inverter Concept           | 60 |

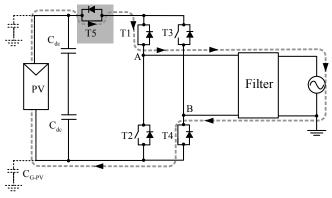

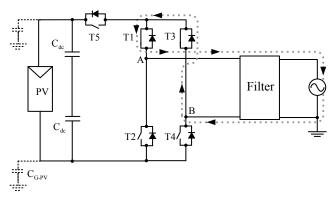

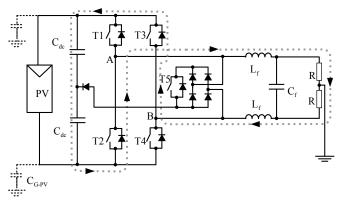

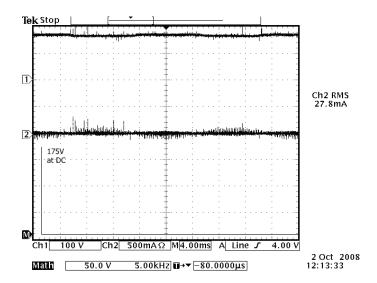

| 5.2.3      | Proposed topology (HB-ZVR)                                       | 62 |

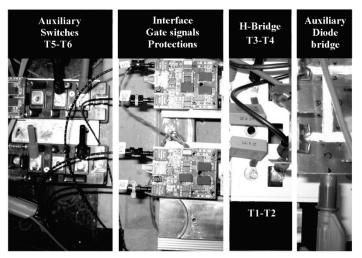

| 5.3        | Experimental results                                             | 65 |

| 5.3.1      | H-Bridge with Unipolar PWM (experiment)                          | 65 |

| 5.3.2      | HERIC (experiment)                                               | 67 |

| 5.3.3      | HB-ZVR (experiment)                                              | 67 |

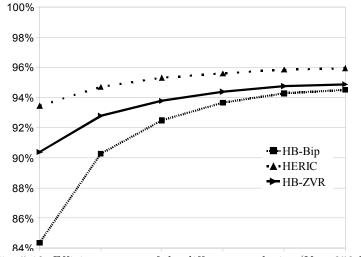

| 5.4        | Efficiency                                                       | 68 |

| 5.5        | Summary                                                          | 70 |

| Chapter 6  | Conclusion                                                       | 71 |

| 6.1        | Summary                                                          | 71 |

| 6.2        | Main contributions                                               |    |

| 6.3        | Future work                                                      | 74 |

| Appendix A |                                                                  | 75 |

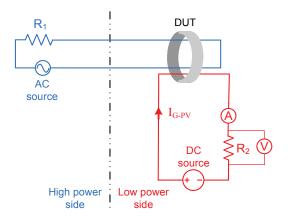

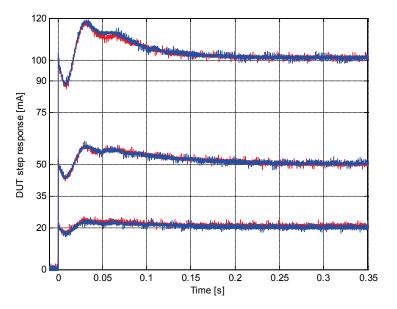

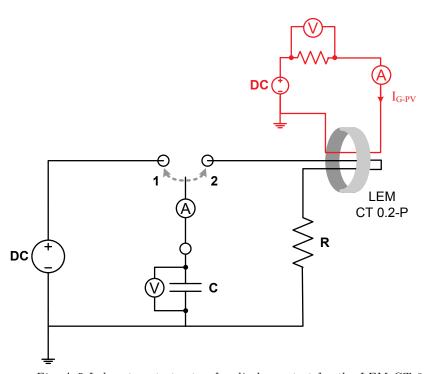

| A.1        | LEM CT-0.2P                                                      | 76 |

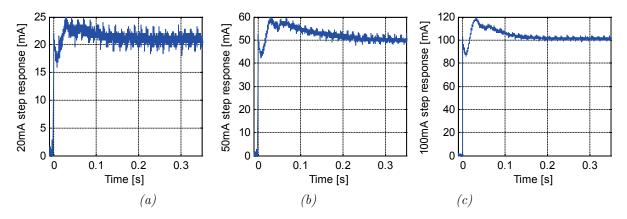

| A.1.1      | Step response                                                    | 76 |

| A.1.2      | Problems                                                         | 78 |

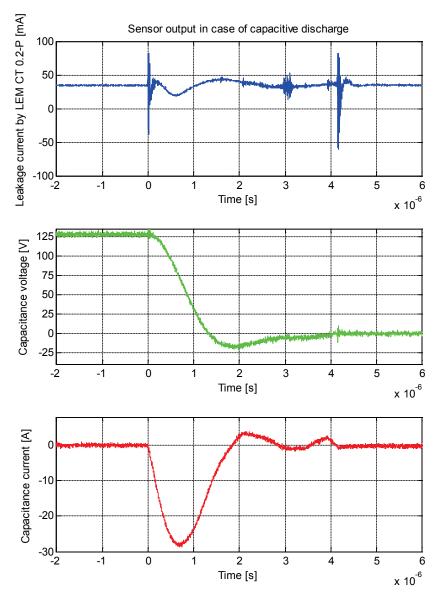

| A.1.3      | "Capacitor discharge" test                                       | 79 |

| A.2        | Telcon HES 25VT sensor test results                              | 80 |

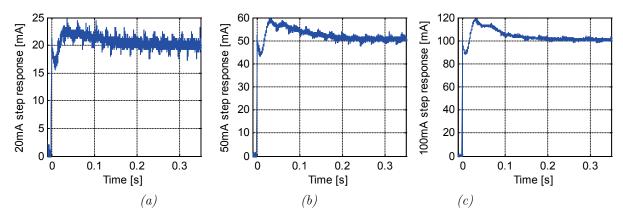

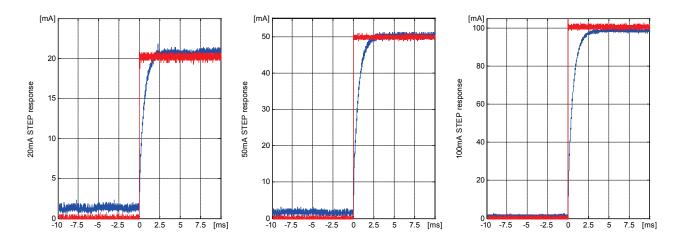

| A.2.1      | Step response                                                    | 81 |

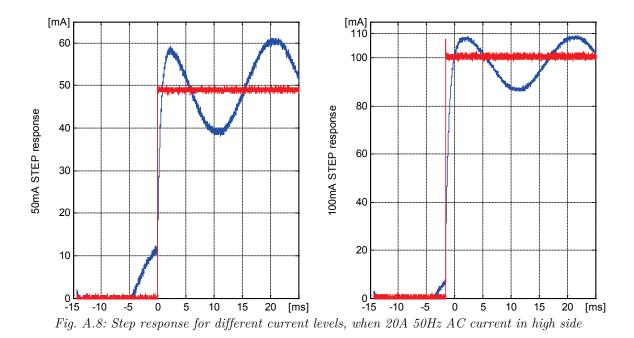

| A.2.2            | Step response with 20A 50Hz AC current in high power side | 81  |

|------------------|-----------------------------------------------------------|-----|

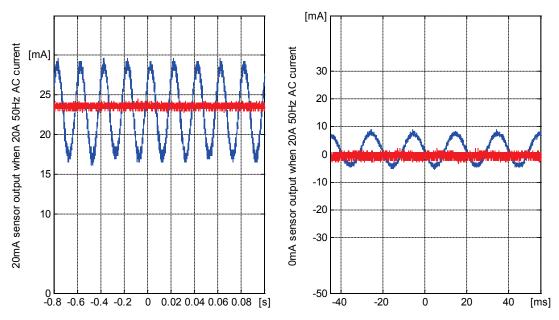

| A.2.3            | Sensor output DC offset                                   | 83  |

| A.2.4            | Sensor output influenced by 50Hz current                  | 83  |

| References       |                                                           | 85  |

| Publications     |                                                           | 91  |

| Publication I    |                                                           | 93  |

| Publication II   |                                                           | 103 |

| Publication III  |                                                           | 111 |

| Publication IV   |                                                           | 119 |

| Publication V    |                                                           | 131 |

| Publication VI   |                                                           | 139 |

| Publication VII. |                                                           | 147 |

|                  |                                                           |     |

|                  |                                                           |     |

## Glossary of terms

3FB Three-phase Full Bridge

3FBSC Three-phase Full Bridge with Split Capacitor

3xNPC Three-phase Neutral Point Clamped

DSP Digital Signal Processor

DUT Device Under Test

EMI Electro Magnetic Interference

FET Field Effect Transistor

FFT Fast Fourier Transform

HB-Bip H-Bridge with Bipolar PWM

HB-Unip H-Bridge with Unipolar PWM

HB-ZVR H-Bridge Zero Voltage Rectifier

HERIC Highly Efficient and Reliable Inverter Concept

HF High Frequency

IEA PVPS International Energy Agency Photovoltaic Power Systems Pro-

gram

IGBT Insulated Gate Bipolar Transistor

LF Low Frequency

MPP Maximum Power Point

MPPT Maximum Power Point Tracker

NPC Neutral Point Clamped

PCC Point of Common Coupling

PF Power Factor

PV Photovoltaic

PWM Pulse Width Modulation

RCMU Residual Current Monitoring Unit

RMS Root Mean Square

SMA Solar Technology AG

THD Total Harmonic Distortion

UPS Uninterruptible Power Supply

VAT Value Added Tax

## Nomenclature list

$\eta$  - conversion efficiency

$\eta_{\scriptscriptstyle E\! U}$  — European efficiency, weighted

$C_{AG}$ ,  $C_{BG}$  and  $C_{CG}$  - stray capacitances between the converter output points and the ground

$C_{dc}$  - DC-link capacitor

$C_f$  - capacitor of output filter

$C_{GPV}$  - parasitic capacitance of PV array

$C_t$  - stray capacitance between the transformer primary and secondary

windings

$f_q$  - grid frequency

$f_{sw}$  - switching frequency of inverter

$f_{sw-LCR}$  - switching frequency of LCR meter

$I_q$  - grid current

$I_{G-PV}$  - ground current through parasitic capacitance of PV panel

$L_A, L_B, L_C \text{ and } L_N \text{ - output filter inductor}$

$L_{cA}$ ,  $L_{cB}$  and  $L_{cC}$  - series inductance of each phase

$L_{cG}$  - inductance between the ground connection of the inverter and the grid

neutral

$L_{cN}$  - series inductance of the neutral

$L_f$  - output filter inductor

$L_q$  - inductance of the grid

R - load resistor

$T_s$  - simulation step time

$V_{ab1},\ V_{bc1}$  and  $V_{ca1}$  - common-mode voltage due to inductor imbalance

$V_{XY}$  - voltage between X and Y, where  $X, Y = \{A, B, C, N\}$  and  $X \neq Y$

$V_{cm}$  - single-phase common-mode voltage

$V_{cmm3}$  - three-phase common-mode voltage

$V_{cmm\text{-}tot}$  - total common-mode voltage

$V_{dc}$  - DC-link voltage for converter

Vdc1 - DC-link voltage for single-phase converter

Vdc3 - DC-link voltage for three-phase converter

$V_q$  - grid peak voltage

$V_{MPP}$  - voltage at maximum power point of PV array

$V_{OC}$  - open circuit voltage of PV array

$V_{out\text{-}LCR}$  - output voltage for LCR meter

## Chapter 1

## Introduction

This chapter presents the background and the motivation of the thesis, continuing with a short overview of grid-connected PV systems. Furthermore, it details the aims of the project, continuing with a list of the main contributions and finishing with the outline of the thesis.

#### 1.1 Background and motivation

The need for a cleaner environment and the continuous increase in energy needs makes decentralized renewable energy production more and more important. This continuously-increasing energy consumption overloads the distribution grids as well as the power stations, therefore having a negative impact on power availability, security and quality [1]. One of the solutions for overcoming this is the Distributed Generation (DG) system. DG systems using renewable energy sources like solar, wind or hydro, have the advantage that the power is produced in close proximity to where it is consumed. This way the losses due to transmission lines are not present.

In the last decade solar energy technologies have become less expensive and more efficient, which have made it to an attractive solution, being cleaner and more environmentally friendly energy resource than traditional ones like fossil fuels, coal or nuclear. Nevertheless, a PV system is still much more expensive than traditional ones, due to the high manufacturing costs of PV panels, but the energy that drives them -the light from the sun- is free, available almost everywhere and will still be present for millions of years, long after all non-renewable energy sources have been depleted.

One of the major advantages of PV technology is that it has no moving parts. Therefore, the hardware is very robust; it has a long lifetime and low maintenance requirements. And, most importantly, it is one solution that offers environmentally friendly power generation [2].

Nowadays, PV panels are not only used in space applications, but they are present in everyday life: powering wrist watches, small calculators, supplying loads in

remote sites and, last but not least, they are connected to the public grid, generating the green power of the future. [3]

#### 1.2 Grid connected PV systems

As mentioned before, decentralized energy production using solar energy could be a solution for balancing continuously-increasing energy needs. Grid connected PV systems have had an enormous increase in their market share over the last decade. With a reasonable set of incentives, the solar photovoltaic market in the U.S. could grow more than 30% per year over the next 20 years, from 340MW of installed capacity to 9600~MW [4]. This market growth is also present in other countries worldwide.

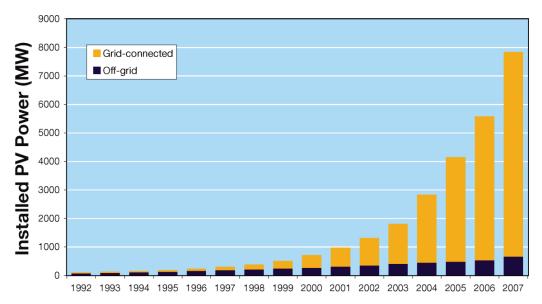

According to the latest report of IEA PVPS on installed PV power, during 2007 there was a total of 2.25~GW of installed PV systems, of which the majority (90%) are installed in Germany, Spain, USA and Japan. At the end of 2007 the total installed PV capacity reached 7.9 GW of which around 92% is grid connected [5] [6].

The growth of installed capacity since 1992 and the split of this capacity between the two primary applications for PV, representing grid connected and stand-alone applications, can be seen in Fig. 1.1.

Fig. 1.1 Cumulative installed capacity between 1992 and 2007 in the IEA-PVPS reporting countries [6].

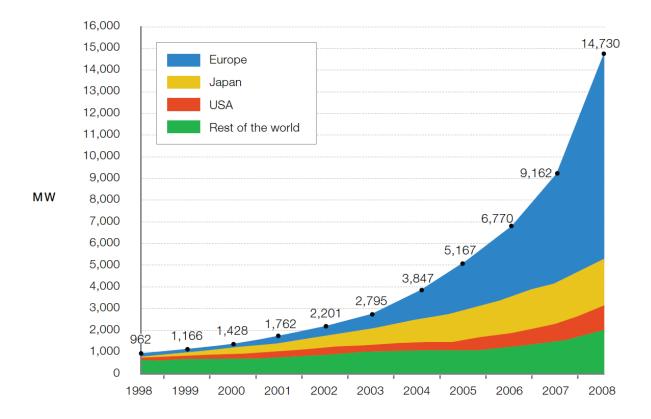

The European solar PV market has increased a lot during these last years. As shown in Fig. 1.2, at the end of 2008 the Global cumulative capacity was just below 15 GW of installed PV, out of which 9 GW, representing 65%, is installed in Europe, followed by Japan with 2.1 GW and USA with 1.2 GW. This European market boom in 2008 is a result of the 2.5 GW of installation in Spain and the 1.5 GW in Germany. Regarding the total PV installations Germany is still leading with 5.3 GW, with Spain

nearing second place with a total of  $3.2 \, GW$ , followed by Japan with  $2.1 \, GW$  and the USA with only  $1.2 \, GW$ , while the rest of the countries are lagging far behind [7].

Fig. 1.2: Historical development of the Global cumulative PV power installed per Region [7].

#### 1.3 Aims of the project

#### 1.3.1 Problem formulation

The efficiency of commercial PV panels is around 15-20%. Therefore, it is very important that the power produced by these panels is not wasted, by using inefficient power electronics systems. The efficiency and reliability of both single-phase and three phase PV inverter systems can be improved using transformerless topologies, but new problems related to leakage current and safety need to be dealt with.

#### 1.3.2 Objectives

The main goal of this project is to analyze and model transformerless PV inverter systems with respect to the leakage current phenomenon that can damage the solar panels and pose safety problems. New topologies and control strategies that will minimize the leakage current and exhibit a high efficiency will be proposed, investigated and verified.

#### 1.3.3 Limitations

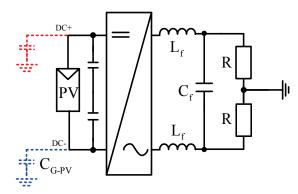

The majority of PV inverters on the market include a boost stage in order to raise the low voltage of the PV array to the needed DC-link voltage of around 400V (single-phase system in Europe) or 700V (three-phase system in Europe). During this research only single stage DC to AC topologies for single- and three-phase grid connection have been studied with a power rating of up to 5-6kW/phase for the low power utility grid. The PV array has been simplified by using a DC power source to rule out the need for a Maximum Power Point Tracker (MPPT), both in simulation and experimental tests. Therefore only a current control strategy has been implemented in the case of grid connection, as presented in Chapter 3. In case the load was a resistive one, to simplify the implementation, only voltage control was used, as detailed in Chapters 4 and 5. The grid has been modeled as an inductance and resistance in series with an ideal sinusoidal voltage source. For simulation the MATLAB/Simulink environment has been used together with the PLECS toolbox, to simulate power electronic circuits. All the active and passive components within the modeled electrical circuit were taken to be ideal.

#### 1.4 Main contributions

A short list of contributions is included in the order they appear in the thesis.

#### Review and simulation of PV topologies

A comprehensive review is presented modeling several single- and three-phase transformerless topologies, focusing on the leakage ground current. It has been shown that the H-Bridge topology with unipolar PWM, as well as the three-phase full bridge topology, generate very high leakage current and are therefore not suitable as transformerless PV inverters. It is also emphasized that connecting the midpoint of the DC-link to the neutral of the grid will substantially reduce the generated leakage current in the case of the half-bridge or neutral-point clamped topologies, although the chosen grid side filter configuration might negatively influence the common-mode behavior of the topology.

#### • Interleaved PWM

The capacitor in the inverters' DC-link tends to get reduced, due to cost reduction from the manufacturers side. This means that the ripple in the DC-link will be increased, leading to higher leakage ground currents through the parasitic capacitance of the PV array. This thesis includes a new application of the interleaved PWM for three-phase inverters that has been modeled in simulation. The ripple of the DC-link voltage is reduced, thereby further reducing the leakage current in case of the three-phase full bridge split capacitor topology.

#### Modeling of common-mode voltage

The leakage current of a certain topology is greatly influenced by the generated common-mode voltage that will be imposed on the parasitic capacitance of the PV array. To show the influence on the common-mode behavior of the topology in the case of inductor unbalance or inductance in the neutral wire, a model-based method for calculating the total common-mode voltage of transformerless topologies has been developed in this thesis.

#### • New topology

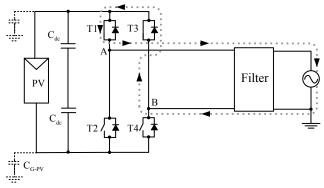

Nowadays, PV inverters feed only active power to the grid, having a power factor of 1. When there are many inverters injecting active power at the same time, the voltage at Point of Common Coupling might rise over the limits stated in the standards and trigger the safety of the inverters leading to disconnection or limit the power production below the available power. To overcome the before-mentioned disadvantage, a new high efficiency transformerless PV inverter topology called HB-ZVR (with very low leakage ground current) is proposed. The topology uses a bidirectional switch for short-circuiting the output of the converter during the zero voltage period using a switch and a diode bridge, capable of active and reactive power injection.

#### 1.5 Outline of the thesis

The need for a cleaner environment and the continuous increase in power demands makes decentralized renewable energy production, like solar and wind, more and more interesting. Decentralized energy production using solar energy could be a solution for balancing the continuously-increasing power demands. This continuously increasing consumption overloads the distribution grids as well as the power stations, therefore having a negative impact on power availability, security and quality. One of the solutions for overcoming this is the grid-connected photovoltaic (PV) system.

PV inverter systems can be improved in terms of efficiency using transformerless topologies, but new problems related to leakage current need to be dealt with.

The work presented in this thesis deals with analyzing and modeling of transformerless PV inverter systems regarding the leakage current phenomenon that can damage solar panels and pose safety problems.

The major task of this research was the investigation and verification of transformerless topologies and control strategies to minimize the leakage current of PV inverter topologies in order to comply with the standard requirements and make them safe for human interaction.

The thesis is divided into two parts: Part I – Report and Part II – Publications. Part I is a summary report of the work done throughout the research and contains 6 chapters.

Chapter 1: Introduction, focuses on the background and motivation regarding the research done in this thesis. Furthermore, the objectives and limitations of the project are enumerated. The chapter finishes with the outline of the thesis.

Chapter 2: Overview of grid connected PV systems, gives an overview about grid connected PV inverters, focusing on transformerless inverters and related safety issues. The parasitic capacitance of several commercial mono- and multi-crystalline PV panels has been measured, and an appropriate value has been defined for use in the simulations. Also, two commercial current sensors that can be used for leakage current measurement, have been tested and the results are presented in Appendix A.

A detailed investigation of different inverter topologies regarding the ground leakage current is described in Chapter 3: Investigation of transformerless topologies, showing the ground voltage and leakage current for the analyzed topologies, concluding with whether the topology is suited for transformerless PV systems.

Chapter 4: Common mode voltage in PV inverter topologies, explains the common-mode behavior of single and three-phase PV inverter topologies by presenting a comprehensive analysis of the single and three-phase transformerless converter with respect to the problem of the leakage current that flows through the parasitic capacitance of the PV array.

In Chapter 5: H-Bridge Zero Voltage Rectifier topology, a new inverter called H-Bridge Zero Voltage Rectifier (HB-ZVR) is proposed, where the mid-point of the DC link is clamped to the grid only during the Zero Voltage period by means of a diode rectifier bridge and one switch. A comparison of known transformerless topologies and the HB-ZVR is performed using simulations, focusing on the voltage to earth harmonics and ground leakage current. Furthermore, experimental results are shown, confirming the simulations, and finally, the efficiency curve of the compared topologies is detailed.

In Chapter 6: Conclusion, the final conclusion is presented, based on the theoretical and experimental results performed. Also a list is given, detailing the contributions presented in this thesis. Additionally, guidelines for future work are given.

The second part of the thesis: Part II – Publications contains the papers that have been published during the period of the research. The articles describe in detail the methods, simulations and the experimental results that make up the backbone of the work described in this thesis.

### 1.6 List of publications

- I. D. Sera, T. Kerekes, R. Teodorescu, PV inverter control using a TMS320F2812 DSP; Proceedings of EDERS 2006; Page(s) 51 57.

- II. M. Ciobotaru, T. Kerekes, R. Teodorescu and A. Bouscayrol, PV inverter simulation using MATLAB/Simulink graphical environment and PLECS blockset IEEE Industrial Electronics, IECON 2006 - 32nd Annual Conference on: 6-10 Nov. 2006; Page(s):5313 - 5318

- III. T. Kerekes, R. Teodorescu and U. Borup, Transformerless Photovoltaic Inverters Connected to the Grid; Twenty Second Annual IEEE Applied Power Electronics Conference, APEC 2007 -; Feb. 25 2007-March 1 2007; Page(s):1733 1737

- IV. T. Kerekes, R. Teodorescu, C. Klumpner, M. Sumner, D. Floricau, P. Rodriguez, Evaluation of three-phase transformerless photovoltaic inverter topologies; European Conference on Power Electronics and Applications, 2007; 2-5 Sept. 2007 Page(s):1 10

- V. T. Kerekes, R. Teodorescu, M. Liserre, R. Mastromauro, A. Dell'Aquila, MPPT algorithm for voltage controlled PV inverters; 11th International Conference on Optimization of Electrical and Electronic Equipment, 2008. OPTIM 2008; 22-24 May 2008 Page(s):427 - 432

- VI. T. Kerekes, R. Teodorescu, M. Liserre, Common mode voltage in case of transformerless PV inverters connected to the grid; IEEE International Symposium on Industrial Electronics, 2008. ISIE 2008. June 30 2008-July 2 2008; Page(s):2390 2395

- VII. A. Dell'Aquila, M. Liserre, R. Mastromauro and T. Kerekes, A Single-Phase Voltage Controlled Grid Connected Photovoltaic System With Power Quality Conditioner Functionality; IEEE Transactions on Industrial Electronics; (accepted for publication)

- VIII. T. Kerekes, R. Teodorescu, M. Liserre, C. Klumpner and M. Sumner, Evaluation of Three-phase Transformerless Photovoltaic Inverter Topologies, IEEE Transactions on Power Electronics (accepted for publication)

- IX. T. Kerekes, R. Teodorescu, P. Rodriquez, G. Vazquez and E. Aldabas, A new high-efficiency single-phase transformerless PV inverter topology; IEEE Transactions on Industrial Electronics (accepted for publication)

## Chapter 2

# Overview of grid connected PV systems

This chapter highlights the advantages of transformerless PV inverters compared to those with galvanic isolation. Furthermore, a summary of several transformerless PV inverter topologies is presented, followed by discussions about the parasitic capacitance of the PV array, emphasizing the safety issues regarding ground leakage currents due to varying voltages imposed over this capacitance.

#### 2.1 Introduction

PV systems connected to the low voltage grid have an important role in distributed generation systems. In order to keep up with the current trends regarding the increase in PV installations, PV inverters should have the following characteristics:

Low cost

- Small weight and size, due to residential installations

- High reliability to match with that of PV panels

- High efficiency

- Be safe for human interaction

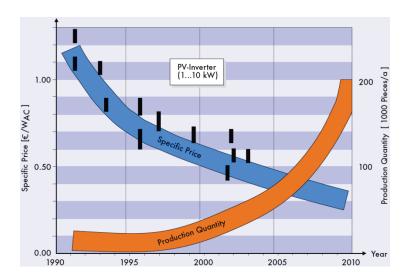

During the last decade PV inverter technologies have evolved a lot. As shown in Fig. 2.1, inverter prices have dropped around 50% during the last two decades and efficiency and reliability have increased considerably [1]. Depending of the power rating of the inverter, the price of inverters below 10~kW varies between 0.2 and 1.2 euro/kW excluding VAT [8]. All this development and improvement happened especially in Europe, USA and Japan. Here one can find many small-scale, building integrated systems that are connected to the grid [9].

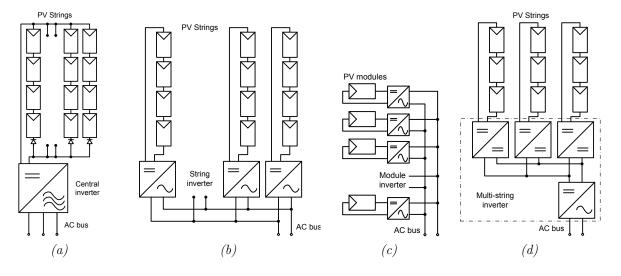

In order to decrease the cost-to-efficiency ratio of PV systems, new inverter designs have been developed. A general classification of grid connected PV inverters is as follows [1], [9], [10], [11], [12], [13], [14]:

- central inverters

- string inverters

- module integrated inverters

- multi-string inverters

Fig. 2.1: Development and prognoses of specific cost and production quantity for a PV-inverter of nominal power between 1 and 10kW during the last two decades [1].

#### 2.1.1 Central inverters

PV plants bigger than  $10 \ kWp$  arranged in parallel strings, are connected to one common central inverter (as shown in Fig. 2.2(a)). At first, line commutated thyristor based inverters were used for this purpose. These were slowly replaced by force commutated inverters using IGBTs, because the efficiency of these inverters is higher and their cost is lower.

However the list of its disadvantages is significant:

- need for high-voltage DC cables between PV panels and inverter

- power losses due to common MPPT

- power loss due to module mismatch

- losses in the string diodes

- reliability of the whole system depends on one inverter

#### 2.1.2 String inverters

String inverters, shown in Fig. 2.2(b), were introduced into the European market in 1995. They are based on a modular concept, where PV strings, made up of series-connected solar panels, are connected to separate inverters. The string inverters are paralleled and connected to the grid. If the string voltage is high enough then no voltage boosting is necessary, thereby improving efficiency. Fewer PV panels can also be used, but then a DC-DC converter or a line frequency transformer is needed for a boosting stage.

The advantages compared to the central inverter are as follows:

- no losses in string diodes (no diodes needed)

- separate MPPTs for each string

- better yield, due to separate MPPTs

- lower price due to mass production

#### 2.1.3 Module inverters

An AC module is made up of a single solar panel connected to the grid through its own inverter, as shown in Fig. 2.2(c). The advantage of this configuration is that there are no mismatch losses, due to the fact that every single solar panel has its own inverter and MPPT, thus maximizing the power production. The power extraction is much better optimized than in the case of String inverters. One other advantage is the modular structure, which simplifies the modification of the whole system because of its "plug & play" characteristic. One disadvantage is the low overall efficiency due to the high-voltage amplification, and the price per watt is still higher than in the previous cases. But this can be overcome by mass production, leading to low manufacturing and retail costs [10].

#### 2.1.4 Multi-String inverters

Multi-String inverters have recently appeared on the PV market. They are an intermediate solution between String inverters and Module inverters. A Multi-String inverter, shown in Fig. 2.2(d), combines the advantages of both String and Module inverters, by having many DC-DC converters with individual MPPTs, which feed energy to a common DC-AC inverter. This way, no matter the nominal data, size, technology, orientation, inclination or weather conditions of the PV string, they can be connected to one common grid connected inverter[15], [16].

The Multi-String concept is a flexible solution, having a high overall efficiency of power extraction, due to the fact that each PV string is individually controlled, as done by the Sunny Boy Multi-String 5000 by SMA.

Fig. 2.2: Different grid-connected PV inverter structures: Central inverter (a); String inverter (b);

Module inverter (c) and Multistring inverter (d).

#### 2.2 Grid requirements

If a PV system is connected to the grid, then the generated power has to comply with specific standards, which are regulated by the utility in each country. The main norms that grid connected inverters have to comply with are:

- Total Harmonic Distortion (THD) and individual harmonic current levels

- Power factor (PF)

- Level of injected DC current

- Voltage and frequency range for normal operation

- Detection of islanding operation (islanding or non-islanding functions)

- Automatic reconnection and synchronizing

- Grounding of the system

International Standards that deal with grid connected photovoltaic systems are the following:

- IEC 60364-7-712:2005. Electrical Installations of Buildings. Part 7: requirements for special installations or locations. Section 712: Photovoltaic power supply systems. [17]

- IEEE 1547.1-2005 IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems. [18]

- UL 1741. Standard for Safety Inverters, Converters, Controllers and Interconnection System Equipment for Use with Distributed Energy Resources. 7<sup>th</sup> May 1999, updated in 2005.

- IEEE 929-2000. Recommended Practice for Utility Interface of Photovoltaic (PV) Systems. [19]

- IEC 61727 (1995-06) Photovoltaic Systems Characteristics of the Utility Interface. [20]

- DS/EN 61000-3-2 (2001) EMC, Limits for harmonic emissions (equipment input current up to and including 16 A per phase) [21]

- VDE0126-1-1 (2006) Selbsstättige Schaltschtelle zwischen einer netzparalellen Eigenerzeugungsanlage und dem öffentlichen Niederspannungsnetz [22]

Most of the above standards are related to the THD and to the individual harmonic levels in the injected current, the frequency deviation of the grid voltage from the standard one, the PF, the normal operating voltage range and the level of the DC current that is injected in the grid. In [10] a comparison of three different standards is made (IEC61727, IEEE1547 and EN61000-3-2), focusing on the previously enumerated issues.

Regarding DC current injection (an important issue in case of grid connected inverters) the following table can be summarized about the requirements set by each standard:

Table 2-1: Limit of the injected DC current, for different standards [10].

|               | IEC61727       | VDE0126-1-1 | IEEE1547     | EN61000-3-2         | IEEE 929-2000      |

|---------------|----------------|-------------|--------------|---------------------|--------------------|

|               |                |             |              |                     |                    |

|               |                |             | < 0.5 % of   | < 0.22 A corres-    |                    |

| $DC\ current$ | < 1 % of rated |             |              |                     | < 0.5 $%$ of rated |

|               |                | < 1 A       | rated output | ponds to a 50 W     |                    |

| injection     | output current |             |              |                     | $output\ current$  |

|               |                |             | current      | half-wave rectifier |                    |

|               |                |             |              |                     |                    |

Furthermore, the VDE 0126-1-1 standard states, that in the case of a DC current injection greater than 1 A, disconnection is mandatory in 0.2 s. The other standards do not mention a requirement for disconnection time.

There is only one standard that specifically deals with transformerless PV systems regarding fault and leakage current levels: the German VDE-0126-1-1 standard.

According to the German standard, there are three different currents that have to be monitored:

- Ground Fault current, which happens in case of insulation failure when the current flows through the ground wire;

- Fault current, which represents the sum of the instantaneous values of the main currents, that in normal conditions leads to zero;

- Leakage Ground currents, which is the result of potential variations of capacitive coupled parasitic elements;

The monitoring is typically done using a Residual Current Monitoring Unit (RCMU), which measures the fault and leakage current of the whole system. The standard states that disconnection from the grid is necessary within 0.3 s in case the leakage current is higher than 300 mA. Furthermore, it recommends a table detailing the Root Mean Square (RMS) value of the fault/leakage current jumps and their respective disconnection times, as detailed in Table 2-2.

| Table 2-2: Leakage current | t jumps and their | corresponding disconnection | times for VDE 0126-1-1 |

|----------------------------|-------------------|-----------------------------|------------------------|

|                            |                   |                             |                        |

| Leakage current jump value | Disconnection time |  |

|----------------------------|--------------------|--|

| (mA)                       | <i>(s)</i>         |  |

| 30                         | 0.3                |  |

| 60                         | 0.15               |  |

| 100                        | 0.04               |  |

As shown in Table 2-2, in cases where the RMS value of the fault/leakage current increases by 30~mA, then disconnection is mandatory within 0.3~s. This way in case of a fault/accident or too high leakage ground current, the system is disconnected and deenergized.

#### 2.3 Transformerless PV inverters

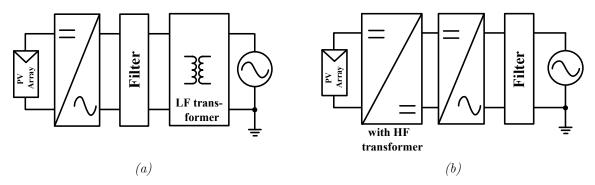

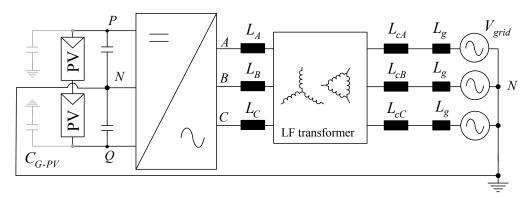

Depending on the electrical isolation between the PV panels and utility grid, the inverter can be isolated or non-isolated. This galvanic isolation is usually realized by the means of a transformer, which has major influence on a grid-connected PV systems' DC to AC efficiency [23]. The presence of the galvanic isolation in a grid connected PV system depends on the local country regulations [24]. In some countries, like the UK and Italy, galvanic isolation is a requirement and is done either by a low-frequency step-up transformer on the grid side or by a high-frequency transformer on the DC side of the converter, as detailed in Fig. 2.3.(a) and (b), respectively.

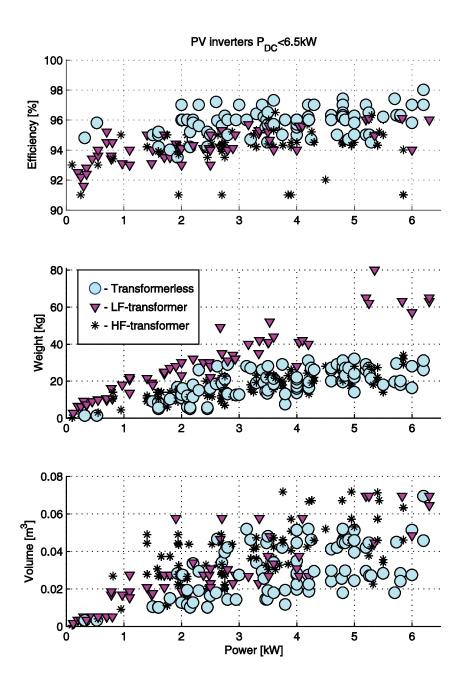

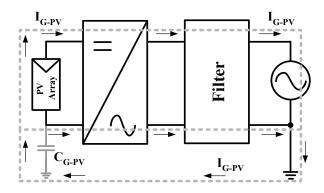

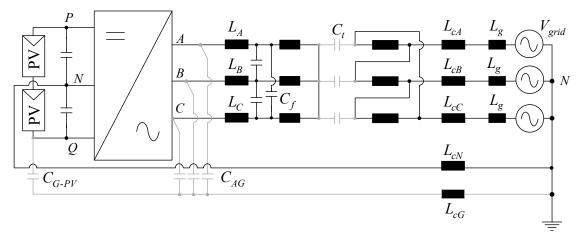

On the other hand, there are countries like Germany and Spain, where the galvanic isolation can be left out, in case another technological solution is used to separate the PV array from the electrical grid [25]. A typical transformerless PV system is detailed in Fig. 2.4, which reduces the weight, size, cost and installation complexity of the whole PV system.

One disadvantage of transformerless systems is that the missing line-frequency transformer can lead to DC currents in the injected AC current by the inverter, which can saturate the core of the magnetic components in the distribution transformer, leading to overheating and possible failure [26],[27].

An important advantage of the transformerless solution is the increase in the total efficiency of the system by approximately 2% [12], [28],[29],[30],[31],[32].

Fig. 2.3: Grid-connected PV system using an inverter with galvanic isolation: grid-side low-frequency

(LF) transformer (a) or DC side high-frequency (HF) transformer (b).

Fig. 2.4: Grid connected PV system with transformerless inverter.

PV inverters usually have two efficiencies reported by the manufacturer: the highest DC-AC conversion efficiency, also called as "Maximum Efficiency", and a weighted efficiency dependent on efficiencies at different irradiation levels, called "European efficiency", based on the formula below [29]:

$$\eta_{EU} = 0.03\eta_{5\%} + 0.06\eta_{10\%} + 0.13\eta_{20\%} + 0.1\eta_{30\%} + 0.48\eta_{50\%} + 0.2\eta_{100\%} \tag{2.1}$$

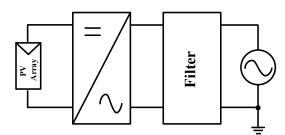

Fig. 2.5 has been made from a database of more than 400 commercially available PV inverters, presented in a commercial magazine about the photovoltaic industry [33], giving details of, amongst other things, the maximum efficiency, weight and size of the different inverters.

Fig. 2.5: PV inverter comparison, based on PHOTON database.

Transformerless inverters are represented by the dots (O), while the stars (\*) represent the topologies including a high-frequency DC-DC transformer and last the triangles  $(\nabla)$  represent the inverters that have a low-frequency transformer on the grid side, adding a galvanic isolation between the PV and grid. It is shown that in the case of PV systems up to 6.5kW, transformerless inverters can reach maximum efficiencies

up to 98%, while inverters with galvanic isolation only have maximum conversion efficiency around 96-96.5%.

The conclusion drawn from these graphs is that the majority of transformerless inverters have higher efficiency, smaller weight and size than their counterparts with galvanic separation.

In the case of Fig. 2.5, the reason for limiting the power up to 6.5kW was the fact that there were only 20 inverters between 6.5 and 15kW and including these in the graph would have influenced the readability of the results.

#### 2.4 Transformerless inverter topologies

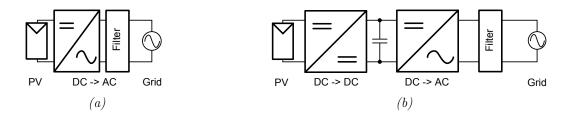

Inverters, according to the levels of power conversion, can have one or more stages. A single and double stage topology for a single-phase grid connection is presented in Fig. 2.6 [34].

Fig. 2.6: Single stage (a) and double stage including voltage boost (b) grid connected PV inverters.

Depending on the voltage level of the PV array, a voltage-boosting stage can be present, which raises the DC-link voltage of the inverter to the required level. This is the case of the two stage topology, where the PV system includes either a DC-DC boost converter, followed by a DC-AC grid side inverter or a step-up transformer on the AC side [35].

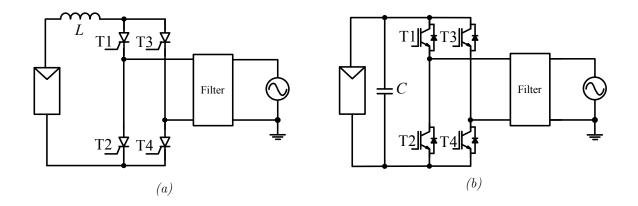

The first PV inverters were based on the technologies used in electrical drives from the beginning of the 1980s. As seen in Fig. 2.7(a), they were line commutated inverters with power ratings of several kW. The major advantages were high efficiency, cheapness and robustness, but the power factor was a major drawback with values between 0.6 and 0.7.

Nowadays inverters are force commutated inverters having power ranges above 1.5kW. A "classic" transformerless topology can be seen on Fig. 2.7(b), having an H-Bridge configuration, usually with switching frequencies greater than 16 kHz to avoid acoustic noise. The efficiency is lower than the line commutated topology, due to the high switching losses. But it is still a robust, cheap and well known technology [36].

Fig. 2.7: Typical single-phase PV inverter, past and present topology, showing a line commutated inverter(a) and an H-Bridge (force commutated) inverter (b) [36].

In case the voltage level from the PV is lower than the required minimum, then a boost converter is added between the PV array and the inverter. This boosts the input voltage from the PV so the inverter has a DC-link voltage around 400~V for single-phase systems and up to 700~V for three-phase grid connection in the European case. Such a single-phase topology can be seen on Fig. 2.8, which differs from Fig. 2.7(b) only by the added boost stage.

Fig. 2.8: Transformerless PV inverter with voltage boost stage [37].

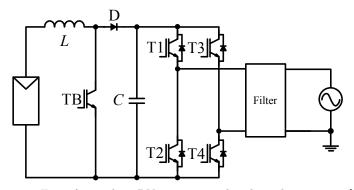

In [38], a similar topology to Fig. 2.8 is proposed for a grid connected PV system. As presented in Fig. 2.9, it is made up of a boost rectifier that raises the voltage of the PV array from  $100 \ V$  to above  $680 \ V$ . This half-bridge topology uses the upper switches in case positive output voltage and the lower switch in case when negative output voltage is required. This topology is used by SMA in their old transformerless inverter Sunny Boy 5000TL Multi-String[16].

Fig. 2.9: Half-bridge topology with voltage boost stage [38].

Having fewer switches in this topology it implies:

- lower conduction losses

- fewer number of components

The disadvantage is that higher input voltage is needed, which increases the rating of the components.

There are also other, more complicated topologies that were summarized in [38] and are a combination of multiple boost or buck-boost single stage inverters.

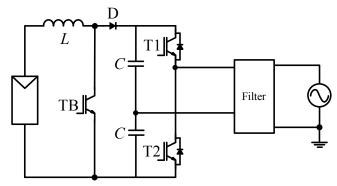

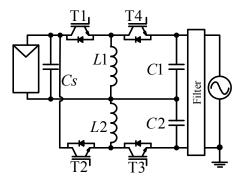

The first topology can be seen on Fig. 2.10 and was proposed by Cáceres and Barbi [39]. The DC inputs of the two identical boost DC-DC converters are connected in parallel with a DC source, such as a PV panel for example. Each one of the converters is modulated to produce a unipolar DC biased sinusoidal output, having a  $180^{\circ}$  phase-shift between each other. This way the output across the load is a pure sinusoidal waveform.

Fig. 2.10: Boost inverter by Cáceres and Barbi [39].

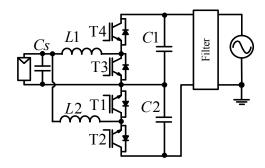

Similarly to the previously presented solution, Vásquez proposed a buck-boost inverter, connecting two buck-boost converters in parallel, the same way as in Fig. 2.10, thereby generating an output voltage either lower or higher than the input. See Fig. 2.11 for details.

Fig. 2.11: Buck-boost inverter topology by Vásquez [40].

Another buck-boost inverter topology, proposed in [41] for a residential PV power system, is able to operate with a wide input voltage range but needs a split DC input source [42]. The topology can be seen in Fig. 2.12. The two converters share the output and operate each half cycle with their own voltage supplies. It is emphasized in [43], that this topology has the inherent nature of common ground for the DC and AC, which makes it suitable for systems where the grounding is required both for the grid neutral and for the distributed power generation resource.

Fig. 2.12: Buck-boost inverter by Kasa [41],[44].

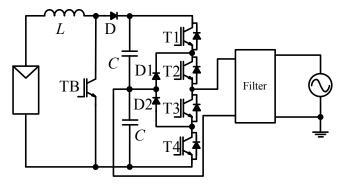

Furthermore, Wang proposed a four-switch resonant buck-boost inverter. The topology can be seen in Fig. 2.13. This zero-current-switching buck-boost inverter operates with switches T1 and T4 and diode D2 in the positive half cycle together with  $L_{r1}$  and  $C_r$  and with T2, T3 and D1 in the negative half cycle together with  $L_{r2}$  and  $C_r$ .

Fig. 2.13: Four-switch resonant buck-boost inverter by Wang [45].

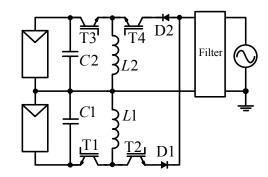

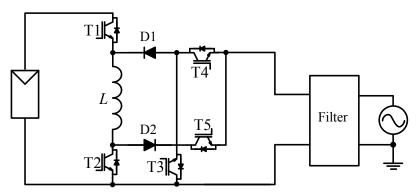

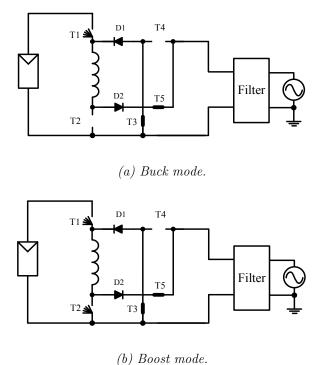

The flying inductor topology patented in [46], reviewed in [37], is shown in Fig. 2.14. It has the advantage of being able to operate in different modes. The positive output current waveform is generated by the converter operating in either buck or boost modes. When the input voltage is higher than the grid voltage, then the inverter operates in buck mode.

Fig. 2.14: Flying inductor inverter[46].

As shown in Fig. 2.15(a), T1 is sine modulated, T2 and T4 are open all the time, T3 and T5 are permanently closed and D1 acts as a freewheeling diode. In the other case, when the input voltage is below the grid voltage, then (as detailed in Fig. 2.15(b)), T1 and T2 are simultaneously sine modulated, T3 and T5 are permanently closed and T4 is open and D1 acts as a freewheeling diode. The negative current waveform is generated by operating the inverter in buck-boost configuration, as shown in Fig. 2.15(c). T1 is sine modulated, T2 and T4 are permanently closed and T3 and T5 are open. D1 acts as a freewheeling diode.

Fig. 2.15: Three different operation modes of the flying inductor inverter.

The main disadvantage of the above topology is the design requirements for the inductor (L), which serves as an energy storage. Magnetic components add to the size and cost of the converter and reduce the overall efficiency. The advantage of this topology is that the negative terminal of the PV array is always connected to grounded grid neutral, thereby fixing the potential of the PV [37]. This topology is used by Siemens in their Sitop Solar Master 1100 PV inverter.

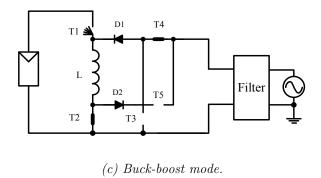

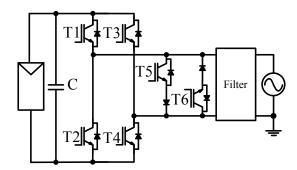

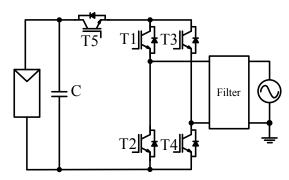

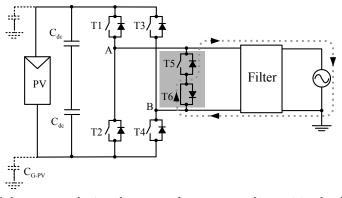

A similar topology to the flying inductor topology is shown in Fig. 2.16 and has been presented in [47]. During the inverting period, when the grid voltage is negative, T1, T3 and T6 are in their conducting state, while T4 and T5 are in their blocking state. T2 is used to shape the output voltage over L2 into a sinusoidal form, using PWM modulation. When the grid voltage is positive, the inverter is in the non-inverting period and T2, T4 and T5 are in their conducting state, while T3 and T6 are blocking. T1 is used to shape the output voltage over L2 using a sinusoidal PWM.

Fig. 2.16: Transformerless PV inverter topology patented by Schekulin [47].

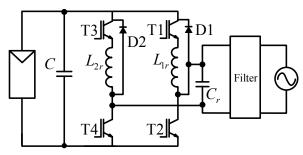

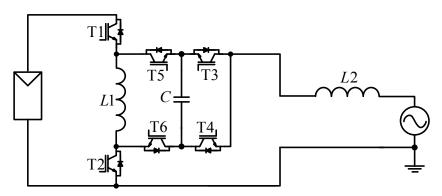

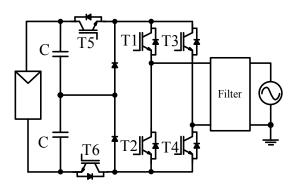

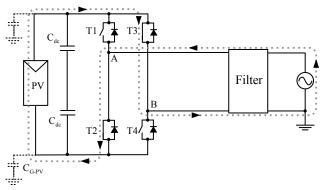

Fig. 2.17 shows a grid connected neutral point diode clamped inverter having a boost stage at its DC input. For the positive current half-wave switches T1 and T2 are used. Turning T2 and T3 ON generates the zero output voltage. And finally, the negative half wave is generated by the pulse-width modulation of T3 and T4. This topology allows the connection of the midpoint of the DC bus to grid neutral, thereby reducing the voltage fluctuations between the PV array and ground [37], [48].

Fig. 2.17: Neutral point diode clamped inverter [37], [49] and [50].

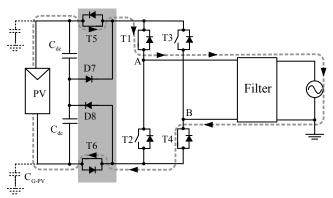

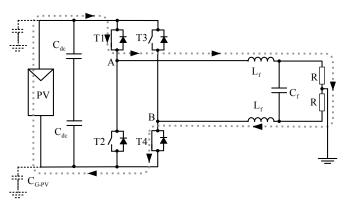

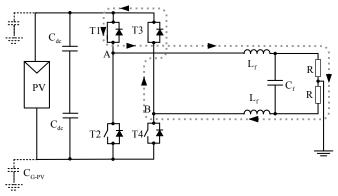

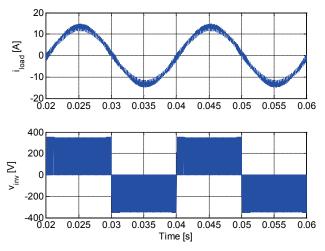

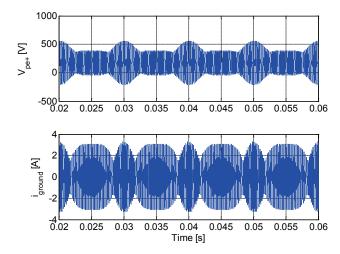

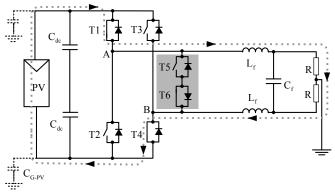

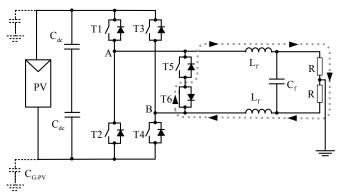

A patented topology shown in [51], called the Highly Efficient and Reliable Inverter Concept (HERIC), uses a modified version of the H-Bridge, by adding two extra switches connected in series with two diodes as shown in Fig. 2.18. The two extra switches (T5 and T6) are used for the freewheeling period and increase the efficiency of the inverter due to the fact that the freewheeling current will not go back to the DC-link capacitor, but it finds a path through T5 or T6 and the respective diode, depending on the sign of the current.

Fig. 2.18: Highly Efficient and Reliable Inverter Concept from Sunways [51].

Another patented inverter topology is again an H-Bridge hybrid. SMA calls it the H5 topology. As detailed in Fig. 2.19, it is made up of a standard H-Bridge topology with an added fifth switch on the DC side. Using this circuit configuration, maximum conversion efficiencies of up to 98% have been reported, depending on the input voltage.

Fig. 2.19: H5 topology from SMA [52].

A similar topology to the previous one is presented in Fig. 2.20, which also uses a modified H-Bridge topology, and adds two extra switches and two diodes. In [53] it is shown that the conversion efficiency of this topology is in the range of 97%, decreasing only in case the input DC voltage is increased above 350V, but even in those cases it stays above 95%.

Fig. 2.20: Transformerless topology by Gonzales et al. [53].

There are several more topologies that have been proposed for transformerless PV inverters in [54],[55],[56], [57], [58] and [59], although their major disadvantage is that they have several conversion stages and need a complex control structure, thereby decreasing the overall conversion efficiency and increasing the complexity and the component count of the inverter.

The PV inverter industry has developed a lot in the last few decades. During these years many transformerless topologies have been proposed, but only a few have been accepted by the industry as suitable topologies for grid-connected PV systems. Therefore, inverters available on the commercial market include the most promising topologies, from the point of view of the structure, complexity, safety, price and efficiency.

#### 2.5 Parasitic capacitance of PV arrays

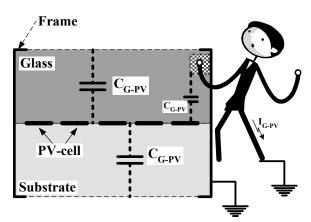

Nowadays most photovoltaic panels have a metallic frame, which is required to be grounded in almost all countries, in order to comply with the safety regulations and standards. Since PV panels have a considerable surface area, this with the metallic frame forms a parasitic capacitance, shown as  $C_{G-PV}$  in Fig. 2.21. The value of this parasitic capacitance depends on the:

- Surface of the PV array and grounded frame

- Distance of PV cell to the module

- Atmospheric conditions

- Dust and humidity, which can increase the electrical conductivity of the panel's surface [2].

In [60] the parasitic capacitance of certain PV panels has been measured to be around 150 pF. If the surface of the panel is fully covered with tap water, the parasitic capacitance increased to 9 nF, approximately 60 times its previous value. According to the measurements the parasitic capacitance varies between 50 nF and 150nF for each kW of installed PV panels. In [60],[61] and [62] the parasitic capacitance has been measured for different PV panels, varying from 100 pF to 3.6  $\mu$ F. It is also mentioned that in the case of thin film modules the measured parasitic capacitance reaches values up to  $1 \mu F/kW$ , due to the metallic sheet on which the cells have been deposited.

In order to have a fairly precise value for simulations, the parasitic capacitance has been also measured for the following multicrystalline PV panels: Soleil FVG 36-125, Kyocera KS10 and BPSolar MSX120.

An HP/Agilent 4284A Precision LCR Meter has been used to measure the series capacitance value, using the following output voltage settings:  $f_{sw-LCR}=10$  kHz,  $V_{out-LCR}=5$  V. The measurements, shown in Table 2-3, have been done by connecting the first terminal of the LCR meter to the output terminal of the PV panel (positive, negative or both short-circuited) and the second terminal of the LCR meter to the frame of the PV panel.

Fig. 2.21: Parasitic capacitance in PV panels [2].

In case of the measurement using someone's palm, the second terminal of the LCR meter was connected to the palm directly, while the whole palm touched the surface of the PV panel. In this case there were two different palms: a copper palm, represented by a copper plate, having the size of an average palm and a normal human palm.

The frequency of the output voltage has been changed for the following values: 1kHz,  $10\ kHz$ ,  $20\ kHz$  and  $50\ kHz$ . No difference has been observed in case of the first set of measurements, representing the case when the PV panels and the palm were dry. The measured parasitic capacitance values were not influenced by the frequency of the voltage.

Furthermore, the atmospheric conditions were changed by covering the surface of the PV panels with moisture and the measurements were repeated, in order to take the readings for the wet case too. The results are summarized also in Table 2-3, and it can be seen that in humid atmospheric conditions the measured values of the parasitic capacitance have significantly increased, in some cases by a factor of 10 or more, depending on the frequency of the imposed voltage.

Table 2-3: Parasitic capacitance measurements.

|                                               | Soleil FVG 36-                                                          | Kyocera KS10                                                            | BPSolar MSX120                                                          |

|-----------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Surface of PV panel                           | 204 <b>x</b> 352 mm <sup>2</sup>                                        | $1197 \times 535 \ mm^2$                                                | 1108 <b>x</b> 991 mm <sup>2</sup>                                       |

| Power at MPP (STC)                            | 80 W                                                                    | 10 W                                                                    | 120 W                                                                   |

| $C_{G\text{-}PV}(1 \ panel)$                  | 130 pF                                                                  | 57 pF                                                                   | 21 pF                                                                   |

| $C_{G\text{-}PV}(1panel)$ wet                 | 2.58 nF @ 1 kHz<br>1.38 nF @ 10 kHz<br>1.12 nF @ 20 kHz                 | 3.44 nF @ 1 kHz<br>2.39nF @ 10 kHz<br>1.99nF @ 20 kHz                   | 9 nF @ 1 kHz<br>3 nF @ 10 kHz<br>2 nF @ 20 kHz                          |

| $C_{G	ext{-}PV}(2panels)$                     | 770 pF @ 50 kHz                                                         | 1.37 nF @ 50 kHz<br>101 pF                                              | 1.15 nF @ 50 kHz  not available                                         |

| $C_{G	ext{-}PV}(1panel+\ palm)$               | 140 pF                                                                  | 150 pF                                                                  | 200 pF                                                                  |

| $C_{G\text{-}PV}$ (1panel+palm) wet           | 215 pF @ 1 kHz<br>185 pF @ 10 kHz<br>175 pF @ 20 kHz                    | 350 pF @ 1 kHz<br>230 pF @ 10 kHz<br>180 pF @ 20 kHz                    | 320 pF @ 1 kHz<br>200 pF @ 10 kHz<br>185 pF @ 20 kHz                    |

| $C_{G\text{-}PV}(1panel+\ copper\ plate)$     | 160 pF                                                                  | 140 pF                                                                  | 150 pF                                                                  |

| $C_{G	ext{-}PV}(1panel+\ copper\ plate)\ wet$ | 219 pF @ 1 kHz<br>210 pF @ 10 kHz<br>208 pF @ 20 kHz<br>205 pF @ 50 kHz | 235 pF @ 1 kHz<br>212 pF @ 10 kHz<br>207 pF @ 20 kHz<br>200 pF @ 50 kHz | 276 pF @ 1 kHz<br>257 pF @ 10 kHz<br>251 pF @ 20 kHz<br>244 pF @ 50 kHz |

This parasitic capacitance is present in every PV installation and may or may not lead to leakage ground current, depending on the existence of the return path within the circuit. Since the value of this parasitic capacitance changes within wide ranges depending on construction, atmospheric conditions, etc., a value of 100 nF/kW has been chosen to be used in simulations, in order to accurately simulate the behavior of the whole PV system, with regards to the ground leakage current. The 100 nF/kW value has been chosen taking into account the worst case scenario in case of a 5 kW PV installation, made up of 40 BPSolar 120MSX panels.

#### 2.6 Leakage ground current

A transformerless topology lacks the galvanic isolation between the PV array and grid. This way the PV panels are directly connected to the grid, which means that

there is a direct path for the leakage ground currents caused by the fluctuations of the potential between the PV array and the grid. These voltage fluctuations charge and discharge the parasitic capacitance formed between the surface of the PV and grounded frame, shown as  $C_{G-PV}$  in Fig. 2.22. The parasitic capacitance together with the DC lines that connects the PV array to the inverter, form a resonant circuit and the resonance frequency of this circuit depends on the size of the PV array and the length of the DC cables [63],[64].

A study, presented in [60] discusses the electrical hazards when a person touches the surface of the PV array. Based on the inverter topology, PV panel structure and modulation strategy, when touching the surface of the panels, a ground current could flow through the human body and if the current is above a certain levels it could lead to a shock or resulting in personal injury, as also discussed in [65], [66]. The path of the ground current  $(I_{G-PV})$  flowing through the parasitic capacitance of the PV array is shown with a grey intermittent line in Fig. 2.22.

Fig. 2.22: Transformerless PV system showing the parasitic capacitance between the PV and the grounded frame of the array and the path of the alternating ground leakage current.

In [60] several recommendations are given, which lead to the minimization of the before mentioned leakage current, by:

- grounding the frame of the PV array, which reduces the capacitance, thereby minimizing the ground leakage current.

- carefully choosing the topology and the modulation strategy, thereby reducing the voltage fluctuations between the PV array and ground.

- disconnecting the inverter under service maintenance.

The VDE0126-1-1 standard recommends the use of a Residual Current Monitoring Unit (RCMU) in order to monitor the safe operation of the grid connected PV system. Several experimental tests have been done in order to test two commercially available current sensors that could be used for ground leakage current measurement.

The LEM CT 0.2-P [67] sensor is a differential current sensor used for current measurements up to 400 mA. The step response tests showed that using this sensor the readings are accurate in all conditions. There are some high frequency oscillations in the sensor output in the case of the high frequency capacitive discharge test, but otherwise the sensor was very accurate and had a steady state error below 5% of the reading. Step response tests had less than 20% overshoot above the reference level and the output stabilized after 0.2 s.

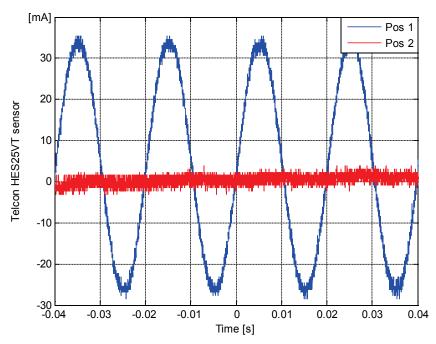

The **Telcon HES 25VT** [68] sensor was also tested for differential current measurement, by modifying the auxiliary circuit based on the suggestions on the supplier's webpage, in order to be able to measure mA currents. Direct currents could be measured accurately. On the other hand, the 50~Hz current influenced the reading and a 50~Hz component was present in the sensor output having amplitude proportional to the level of the 50~Hz current. The influence was further investigated and it was found out that the position of the wires relative to the Hall sensor is very important and the output of the sensor is very sensitive to this position.

The details regarding these tests are included in Appendix A.

#### 2.7 Summary

This chapter shows the advantages of transformerless PV inverters compared to topologies with galvanic isolation. It is shown that transformerless topologies are smaller in size and have higher efficiencies than inverters with high-frequency or low-frequency transformers. Furthermore, a summary of several transformerless PV inverter topologies is presented, detailing the many different topology structures that are used by the PV industry or have been proposed as transformerless PV inverters. Finally the parasitic capacitance of the PV array is discussed and measured in case of several commercial PV panels, emphasizing the safety issues regarding ground leakage currents due to varying voltages imposed over this capacitance.

### Chapter 3

# Investigation of transformerless topologies

In this chapter the modeling of several transformerless grid connected topologies is done. For each case the voltage to ground and leakage ground current is measured and, based on the result, a conclusion is given regarding the use of such a topology in transformerless grid-connected PV systems.

#### 3.1 Introduction

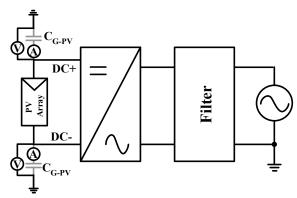

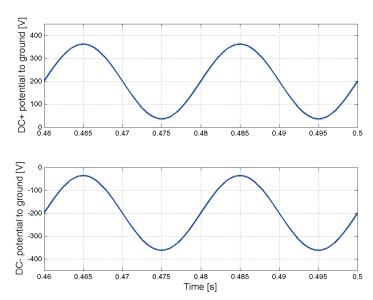

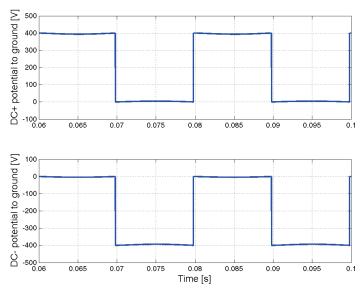

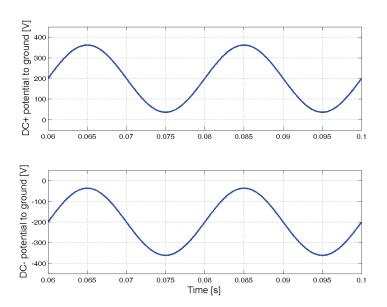

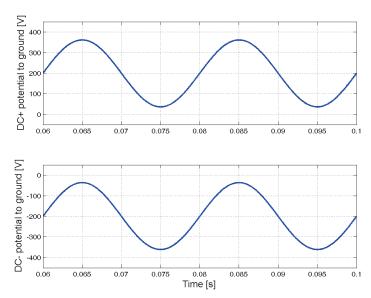

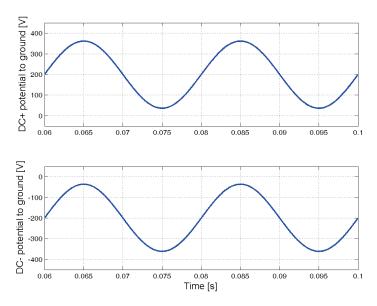

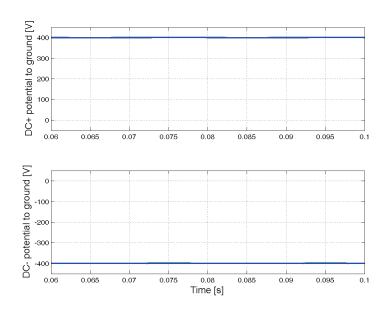

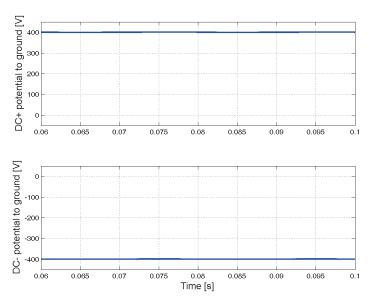

The voltage to ground is measured across  $C_{G-PV}$ , between the DC+ and ground respectively, DC- and ground terminals of the PV array, as shown in Fig. 3.1. The parasitic capacitance of the PV array is modeled using a simple capacitor, through which the leakage current finds its path to ground. This leakage current is measured and, based on these results, an individual conclusion is drawn for each topology.

Fig. 3.1: Voltage to ground and leakage ground current measurement setup.

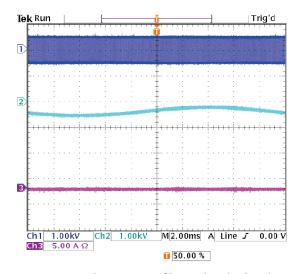

Simulations were done in MATLAB Simulink with the PLECS toolbox, used to model the electrical part of the system, as detailed in Publication II. The implemented control strategy is described in Publication I. The simulation parameters are given in Table 3-1.

| Simulation step size                            | $T_s$ =2,5e-7 s (250 ns) |

|-------------------------------------------------|--------------------------|

| Switching frequency                             | $f_{sw}=10 \ kHz$        |

| Single phase DC voltage                         | Vdc1=400 V               |

| Three-phase DC voltage                          | Vdc3=700 V               |

| DC-link capacitance                             | $C_{dc}=1 \ mF$          |

| Output filter inductance                        | $L_f=1.8~mH$             |

| Output filter capacitance                       | $C_f=2~\mu F$            |

| Grid voltage (peak of phase to neutral voltage) | $V_g=325 \ V$            |

| Grid frequency                                  | $f_g$ =50 Hz             |

| Grid inductance                                 | $L_g = 50 \ \mu H$       |

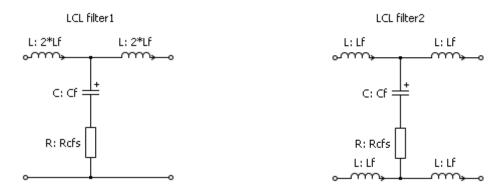

Two LCL filter configurations can be considered for the grid side filter, as presented in Fig. 3.2, having inductor  $L_f$  only in the line branch or like in Fig. 3.3, having inductor  $L_f$  split equally between the line and neutral branches. The current ripple is identical for both, although the leakage current is greatly influenced by the filter configuration, as will be shown in the simulations. Only the LCL configuration has been used for the grid side filter, because it has the advantage over the  $L_f$  and LC filter configurations that it reduces the dependence on grid parameters by providing a better decoupling between the filter and grid impedance [69].

Fig. 3.2: LCL filter configuration (case 1).

Fig. 3.3: LCL filter configuration (case 2).

The simulations include the following topologies:

- Single-phase:

- o H-Bridge with bipolar modulation

- o H-Bridge with unipolar modulation

- H-Bridge with hybrid modulation

- o H-Bridge with AC bypass (HERIC)

- o H-Bridge with DC bypass (H5-SMA)

- o H-Bridge with DC bypass (6 switches)

- o Half-Bridge

- o Neutral Point Clamped

- Three-phase inverter

- o Three-phase Full-Bridge

- o Three-phase Full-Bridge with split capacitor

- Three-phase Full-Bridge with split capacitor using staggered modulation

- o Three-phase Neutral Point Clamped

#### 3.2 Single-phase topologies

Single-phase systems are mostly used in the private sector. The majority of such PV systems can have up to 5kW and are roof mounted with a fixed tilt and a southward orientation.

#### 3.2.1 H-Bridge topology with Bipolar PWM

The H-Bridge is a well-known topology and it is made up of two half bridges. This topology has also been used in motor drives or UPS applications. To control the four switches of this topology several PWM techniques can be implemented. The simplest one is the bipolar PWM [70], which modulates switches T1-T4 (Fig. 3.4) complementary to T2-T3 (Fig. 3.5), resulting in a two level output voltage  $(+V_{DC})$  and  $-V_{DC}$ . The conversion efficiency is reduced due to the fact that during the freewheeling period the grid current finds a path and flows back to the DC-link capacitor.

Fig. 3.4: T1-T4 turned-ON, for  $+V_{DC}$  output voltage.

Fig. 3.5: T2-T3 turned-ON, for -V<sub>DC</sub> output voltage.

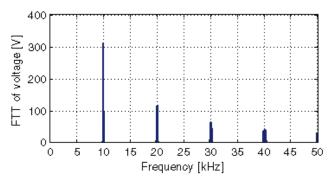

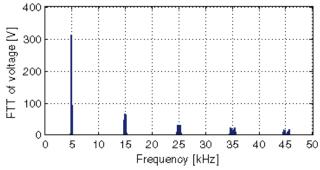

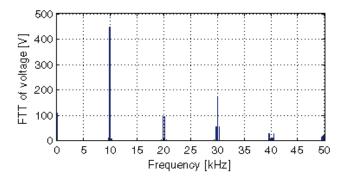

Fig. 3.6 shows an FFT of the voltage to ground of the PV array when the grid side filter has the inductors only in the line side. In this case there are high frequency components at the switching frequency and multiples of it, having very high amplitudes. If these high frequency voltage fluctuations are imposed on the parasitic capacitance of the PV array, then the leakage current will be very high and the exact value of the current will depend only on the value of the parasitic capacitance ( $C_{G-PV}$ ). Therefore it can be said, that this particular case with such a filter configuration is not suitable for transformerless PV systems.

Fig. 3.6: Simulation results, FFT of voltage to ground having a bipolar PWM (grid side filter is according to case 1 from Fig. 3.2).